## Effects of interface state charges on the electrical properties of Si/SiC heterojunctions

J. Liang, S. Nishida, T. Hayashi, M. Arai, and N. Shigekawa

Citation: Applied Physics Letters 105, 151607 (2014); doi: 10.1063/1.4898674

View online: http://dx.doi.org/10.1063/1.4898674

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/15?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Effects of thermal annealing process on the electrical properties of p+-Si/n-SiC heterojunctions Appl. Phys. Lett. **104**, 161604 (2014); 10.1063/1.4873113

Interface characteristics of n - n and p - n Ge/SiC heterojunction diodes formed by molecular beam epitaxy deposition

J. Appl. Phys. 107, 124512 (2010); 10.1063/1.3449057

Capture cross sections of defect states at the Si/SiO 2 interface

J. Appl. Phys. 88, 842 (2000); 10.1063/1.373746

Significance of tunneling in p + amorphous silicon carbide n crystalline silicon heterojunction solar cells Appl. Phys. Lett. **73**, 2609 (1998); 10.1063/1.122521

Observation of multiple defect states at silicon–silicon nitride interfaces fabricated by low-frequency plasmaenhanced chemical vapor deposition

Appl. Phys. Lett. 71, 252 (1997); 10.1063/1.119512

## Effects of interface state charges on the electrical properties of Si/SiC heterojunctions

J. Liang, <sup>1,a)</sup> S. Nishida, <sup>1</sup> T. Hayashi, <sup>1</sup> M. Arai, <sup>2</sup> and N. Shigekawa <sup>1</sup> Department of Electrical Engineering, Osaka City University, Sugimoto 3-3-138, Sumiyoshi, Osaka 558-8585, Japan

<sup>2</sup>New Japan Radio Co., Ltd., Fukuoka 2-1-1, Fujimino, Saitama 356-8510, Japan

(Received 22 July 2014; accepted 6 October 2014; published online 17 October 2014)

Electrical properties of p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, p<sup>+</sup>-Si/n<sup>-</sup>-SiC, and n<sup>+</sup>-Si/n<sup>-</sup>-SiC heterojunctions fabricated by using surface-activated bonding are investigated. Their flat-band voltages obtained from capacitance-voltage (C-V) measurements are found to be  $\sim$ 0.92 eV, which suggests that the Fermi level should be pinned at the bonding interface. An analysis by using the charge neutral level model reveals that the C-V characteristics are sensitive to the density of interface states. The measured C-V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions are in quantitative agreement with modeled ones obtained for the interface states density and the conduction-band discontinuity of  $2.3 \times 10^{13} \, \text{cm}^{-2} \, \text{eV}^{-1}$  and  $0.3 \, \text{eV}$ , respectively. ©  $2014 \, AIP \, Publishing \, LLC$ . [http://dx.doi.org/10.1063/1.4898674]

Silicon carbide (SiC) based devices are promising as the next generation power devices because of its unique physical properties such as a wide band gap, a high thermal conductivity, a high electron saturation velocity, the high physical and chemical stability, and a high breakdown field. The combination of SiC with Si technologies has potential application for bipolar transistors with wide band gap emitters, <sup>2,3</sup> switching devices, <sup>4</sup> electroluminescence devices, <sup>5</sup> and sensors. In growing SiC layers on Si, <sup>7</sup> because of the large lattice mismatch and difference in thermal expansion coefficients between Si and SiC, a marked residual stress and defects with high densities are frequently encountered, which limits the intrinsic performance of grown Si/SiC heterojunctions. <sup>8</sup>

One way to overcome these difficulties is direct wafer bonding such as hydrophilic wafer bonding of and surface-activated bonding (SAB). In SAB, surfaces of substrates are activated by the fast atom beams of Ar prior to bonding, which enables us to bond substrates without heating them. However, interface states with high densities are likely to be formed in the SAB process since dangling bonds are unveiled on sample surfaces due to the irradiation of Ar atom beams. It was pointed out that such interface states modified potential barriers at the interface of n-GaP/n-InGaP<sup>14</sup> and p-GaAs/n-GaN junctions. In n-n and p-n Ge/SiC heterojunction diodes, the interface states caused the pinning of Fermi-level.

Reported conduction band discontinuities in Si/SiC heterojunctions are largely scattered between 0.21 and 1.9 eV.<sup>7,18</sup> This suggests that the electrical properties of the Si/SiC heterojunctions should be largely varied by the possible interface states. The impact of the interface states to the electrical properties of Si/SiC junctions has not yet been fully understood.

In this letter, we report on the electrical properties of Si/SiC heterojunctions fabricated by using SAB. We measured their current-voltage (I-V) and capacitance-voltage (C-V)

We used four types  $(p^-, p_-, p^+, and n^+)$  of (100) Si substrates and n<sup>-</sup>-4H-SiC epitaxial substrate. Their carrier concentrations are shown in Table I. The carrier concentrations of Si substrates were estimated by Hall measurements at room temperature. Al/Ni/Au multilayers were evaporated on the backsides of p<sup>-</sup>-, p- and p<sup>+</sup>-Si substrates and n<sup>-</sup>-SiC epitaxial substrates, respectively. The ohmic contacts of ptype Si and n-type SiC were formed by a rapid thermal annealing at 400 and 1000 °C for 60 s in N<sub>2</sub> gas ambient, respectively. Then, we bonded each of the p-type substrates to the SiC epitaxial substrates so that p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, and p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions were fabricated. n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions were fabricated by evaporating Ti/Au multilayers on the backsides of n<sup>+</sup>-Si substrates after the bonding. All of the four junctions were diced into 4 mm<sup>2</sup> pieces. A Ni/n<sup>-</sup>-SiC Schottky diode was fabricated by deposition of 100 nm nickel film on the surfaces of n-SiC substrates. Prior to Schottky contact deposition, the ohmic contacts of substrates were formed. Their I-V and C-V characteristics were measured using an ADCMT 6242 Source Measurement Unit and an Agilent E4980A Precision Impedance Analyzer, respectively.

TABLE I. The carrier concentration and the thickness of substrates.

| Type                   |                 | Carrier concentration $\mathrm{cm}^{-3}$ | Thickness $\mu$ m |

|------------------------|-----------------|------------------------------------------|-------------------|

| p <sup>-</sup> -Si     |                 | $1.39 \times 10^{15}$                    | 525               |

| p-Si                   |                 | $2.43 \times 10^{17}$                    | 525               |

| p+-Si                  |                 | $2.64 \times 10^{19}$                    | 525               |

| n+-Si                  |                 | $2.61 \times 10^{19}$                    | 525               |

| n <sup>-</sup> -4H-SiC | Epitaxial layer | $\sim 5 \times 10^{15}$                  | 2.8               |

|                        | Buffer layer    | $\sim 1 \times 10^{18}$                  | 0.5               |

|                        | Substrate       | $\sim 1 \times 10^{19}$                  | 235               |

characteristics. Furthermore, we analyzed the influence of charges in the interface states on the electrical characteristics of  $p^+\text{-Si/n}^-\text{-SiC}$  and  $n^+\text{-Si/n}^-\text{-SiC}$  junctions by using the charge neutral level (CNL) model.  $^{19}$

a)E-mail address: liang@elec.eng.osaka-cu.ac.jp

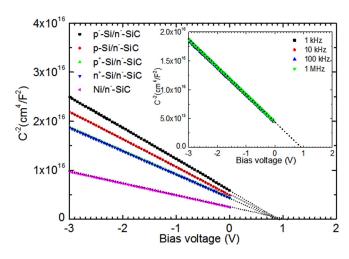

FIG. 1. C-V characteristics of p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, p<sup>+</sup>-Si/n<sup>-</sup>-SiC, n<sup>+</sup>-Si/n-SiC, and Ni/ n-SiC junctions measured at room temperature. The inset shows C-V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions measured at room temperature and frequencies ranging from 1 kHz to 1 MHz.

The  $I/C^2$ -V characteristics of p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, p<sup>+</sup>-Si/n<sup>-</sup>-SiC, n<sup>+</sup>-Si/n<sup>-</sup>-SiC, and Ni/n<sup>-</sup>-SiC junctions measured at room temperature and a frequency of 10 kHz are shown in Fig. 1. The characteristics indicated a straight line and the flat band voltages were found to be 0.92, 0.88, 0.92, and 0.92 V for p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, p<sup>+</sup>-Si/n<sup>-</sup>-SiC, and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, respectively, by linearly extrapolating  $I/C^2$  to zero. It is noteworthy that the flat band voltages are  $\sim 0.9 \, \text{V}$ , irrespective of the polarity and the doping concentrations of Si substrates. The estimated flat band voltage is markedly small in comparison with previous reports  $(\sim 2 \text{ V})$  for n-Si/n-SiC<sup>7,20</sup> and p-Si/n-SiC<sup>9</sup> heterojunctions. The inset shows the  $1/C^2$ -V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions measured at room temperature and frequencies between 1 kHz and 1 MHz. The frequency dispersion was not observed on the bias voltage between -3 and  $0\,\mathrm{V}$ . Similar to p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, the frequency dispersion was also not observed in n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions (not shown in this figure). Using the slopes of  $I/C^2$ -V characteristics, the donor concentrations of the n-SiC epitaxial layer were estimated to be  $3.10 \times 10^{15}$ ,  $3.12 \times 10^{15}$ , and  $6.52 \times 10^{15}$  cm<sup>-3</sup>, for p+-Si/n--SiC, n+-Si/n--SiC, and Ni/n--SiC junctions, respectively.

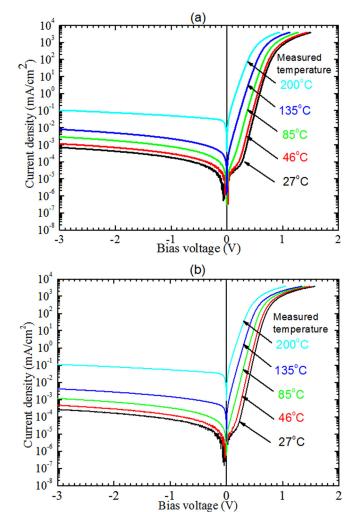

The *I-V* characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions measured at various temperatures are shown in Figs. 2(a) and 2(b), respectively. The respective curves revealed rectifying properties similarly to those in conventional pn junctions. The reverse-bias current increased with increasing the bias voltage and the temperature of the measurement in each junction. It is noteworthy that the I-V characteristics of the two junctions at each temperature are similar to each other. The activation energy of the reversebias current at -3 V was estimated to be 0.37 and 0.39 eV for p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, respectively.

The flat-band voltage  $V_d$  is expressed as

$$qV_d = E_{gp} + \Delta E_c - \delta_{n-sic} - \delta_{p-si}, \qquad (1)$$

FIG. 2. Temperature dependence of the *I-V* characteristics of (a) p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions and (b) n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions.

$$qV_d = \Delta E_c - \delta_{n-sic} + \delta_{n-si}, \qquad (2)$$

for p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, respectively. Note that q is the elementary charge,  $E_{gp}$  is the energy gap of p<sup>+</sup>-Si,  $\Delta E_c$  is the conduction-band discontinuity, and  $\delta_{p-si}$ ,  $\delta_{n-si}$ , and  $\delta_{n-sic}$  refer to the position of the Fermi level relative to the valence-band maximum in p<sup>+</sup>-Si, relative to the conduction-band minimum in n<sup>+</sup>-Si and relative to the conduction-band minimum in n<sup>-</sup>-SiC, respectively. Here, we assumed that no electric charges are placed at the interface. From these expressions,  $\Delta E_c$  was estimated to be 0.05 and 1.09 eV for the p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, respectively. The disagreement in  $\Delta E_c$  between the two junctions, which stems from the result that the flat band voltages of the junctions were close to each other, suggests that interface states with high densities are formed at the bonding interfaces and the Fermi level is pinned.

In analyzing the influence of the interface charges on the C-V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, we assume the followings: (1) The interface states are uniformly distributed in the overlap of band gaps of SiC and Si layers. Their density  $(D_{it})$  is, consequently, independent of their energy. (2) Carriers trapped in the interface states are in thermal equilibrium with those in Si layer, i.e., the Fermi level in the interface states coincides with that in Si layers

irrespective of bias voltages. (3) The distribution of charges in Si layer is locally determined by solving Poisson's equation, and the distribution of charges in SiC layer is estimated by using the space charge in the depletion layer. (4) The sum of the sheet charge densities in the entire junctions is zero.

For p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, interface-state charge density ( $Q_{it}$ ) can be defined as

$$Q_{it} = Q_{Dit} + Q_{Ait} = qD_{it} \int_{0}^{E_{CNL}} (1 - F_{it})dE - qD_{it} \int_{E_{CNL}}^{E_{gp}} F_{it}dE,$$

(3)

where  $Q_{Dit}$  and  $Q_{Ait}$  are positive charge density in the donor-like states and negative charge density in the acceptor-like states, respectively. The energy of CNL  $E_{CNL}$  is preset as  $0.36 \,\mathrm{eV}^{21}$  above the valence band edge of Si. The state occupation function  $F_{it}$  is given by

$$F_{it} = \frac{1}{\exp((E - E_{FP})/kT) + 1},$$

(4)

where  $E_{FP}$  is the Fermi level in  $p^+$ -Si, k is the Boltzman constant, and T is the temperature. Note that  $Q_{it}$  is determined when the surface potential in the  $p^+$ -Si layer  $\psi_s$  is given. The charge per unit area in the  $p^+$ -Si layer  $Q_{p-si}$  is also obtained for a given  $\psi_s$ .<sup>21</sup> Noting that the total charge per unit area must be equal to zero, the depletion layer thickness W is expressed as

$$W = \frac{-(Q_{p-si} + Q_{it})}{qN_{n-sic}},\tag{5}$$

using the donor concentration  $N_{n\text{-}sic}$  of n<sup>-</sup>-SiC epitaxial layer which was obtained from the C-V characteristics of Ni/n<sup>-</sup>-SiC junctions. Furthermore, the bias voltage is expressed using the above parameters (not shown). Thus, the relationship between capacitance and bias voltage is numerically calculated. The C-V characteristics in the n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions are obtained in similar manners.

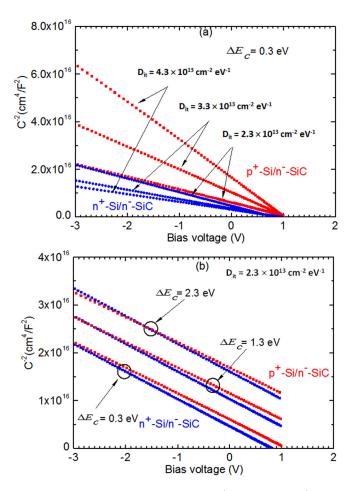

The  $I/C^2$ -V characteristics obtained using a variety of  $D_{it}$ values ranging between  $2.3 \times 10^{13}$  and  $4.3 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> with  $\Delta E_c$  of 0.3 eV are shown in Fig. 3(a).  $I/C^2$  in the n<sup>+</sup>-Si/ n<sup>-</sup>-SiC junctions decreases as  $D_{it}$  increases. In the p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, in contrast,  $I/C^2$  increases as  $D_{it}$  increases. We find that  $I/C^2$ -V characteristics of the two junctions are close to each other for  $D_{it}$  of  $2.3 \times 10^{13} \,\mathrm{cm}^{-2}\,\mathrm{eV}^{-1}$ . The  $1/C^2$ -V characteristics of the two junctions obtained for  $D_{it}$  of  $2.3 \times 10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$  with a variety of  $\Delta E_c$  are shown in Fig. 3(b). The flat band voltage of the two junctions is shifted in accordance with the change in  $\Delta E_c$ . The  $I/C^2$ -V characteristics are close to the measurements when  $D_{it}$  and  $\Delta E_c$  are  $2.3 \times 10^{13} \, \mathrm{cm}^{-2} \, \mathrm{eV}^{-1}$  and  $0.3 \, \mathrm{eV}$ , respectively. The estimated  $\Delta E_c$  is similar to a previous report for Si/SiC junctions<sup>20</sup> that were fabricated by plasma-enhanced chemical vapordeposition. We find that the obtained  $D_{it}$  is much larger than a previously reported one for Si/SiC heterojunctions fabricated by direct wafer bonding.<sup>22</sup> In spite of such large  $D_{it}$  values, the result that frequency dispersions were negligible in the C-V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions [see the inset of Fig. 1] suggests that SAB-based Si/SiC junctions with

FIG. 3. The calculated C-V characteristics of p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions with different (a)  $D_{it}$  and (b)  $\Delta E_c$  values.

heavily-doped Si layers might be applicable for novel devices. Given that the amorphous layer at the bonding interface induces  $D_{it}$ , it should be reduced by thinning the amorphous layer. According to our previous report, <sup>10</sup> the amorphous layer becomes thin with increasing the annealing temperature and finally vanishes after annealing at  $1000 \,^{\circ}$ C.

Based on these estimations, the energy-band diagrams for p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions are depicted. The band diagrams at bias voltages of 0 and -3 V of the respective junctions are shown in Figs. 4(a) and 4(b). We find by comparing the two figures that the band profiles in the SiC layers of the respective junctions are similar to each other. Consequently, the results of the I-V measurements that (1) the entire *I-V* characteristics of the p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions are close to each other irrespective of the ambient temperatures and (2) the activation energy of the reverse-bias current is close to each other (0.37 and 0.39 eV at -3 V for the p<sup>+</sup>-Si/n<sup>-</sup>-SiC and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions, respectively) suggest that the reverse-bias current occurs due to (1) the thermal excitation of electrons from the valenceband (conduction-band) edges in the p<sup>+</sup>-Si (n<sup>+</sup>-Si) layers of the respective junctions and (2) the subsequent tunneling process across the SiC depletion layer.

In summary, we fabricated p<sup>-</sup>-Si/n<sup>-</sup>-SiC, p-Si/n<sup>-</sup>-SiC, p<sup>+</sup>-Si/n<sup>-</sup>-SiC, and n<sup>+</sup>-Si/n<sup>-</sup>-SiC junctions using surface activated bonding and measured their electrical properties at

FIG. 4. Energy band diagrams for (a)  $p^+\mbox{-Si/n}^-\mbox{-SiC}$  and (b)  $n^+\mbox{-Si/n}^-\mbox{-SiC}$  junctions.

room temperature. The temperature dependence of the I-V characteristics for  $p^+\text{-}Si/n^-\text{-}SiC$  is alike to  $n^+\text{-}Si/n^-\text{-}SiC$  junctions. We found that the flat band voltages of all Si/SiC junctions were estimated to be  $\sim 0.92\,\text{eV}$ , which is attributed to Fermi-level pinning at the bonding interface. The influence of the interface state charges on the C-V characteristics of  $p^+\text{-}Si/n^-\text{-}SiC$  and  $n^+\text{-}Si/n^-\text{-}SiC$  junctions was analyzed using the charge neutral level model. The modeled C-V characteristics of  $p^+\text{-}Si/n^-\text{-}SiC$  and  $n^+\text{-}Si/n^-\text{-}SiC$  junctions are sensitive to the density of interface states and the conduction-band discontinuity. They are in agreement with the experimental results when the interface state density and the conduction-band discontinuity are  $2.3 \times 10^{13}\,\text{cm}^{-2}\,\text{eV}^{-1}$  and  $0.3\,\text{eV}$ , respectively. The estimated band profiles of

junctions are consistent with the features of their *I-V* characteristics.

This work was partly supported by "Creative research for clean energy generation using solar energy" project in Core Research for Evolutional Science and Technology (CREST) programs of the Japan Science and Technology Agency (JST).

<sup>1</sup>J. Scofield, H. Kosai, B. Jordan, S.-H. Ryu, S. Krishnaswami, F. Husna, and A. Agarwal, *Proceedings of the ECSCRM 2006 Conference* (Trans Tech Publications, 2007), Vol. 556.

<sup>2</sup>T. Sugii, T. Ito, Y. Furumura, M. Doki, F. Mieno, and M. Mada, J. Electrochem. Soc. **134**, 2545 (1987).

<sup>3</sup>C. W. Liu and J. C. Sturm, J. Appl. Phys. **82**, 4558 (1997).

<sup>4</sup>S. S. Sheng, M. G. Spencer, X. Tang, P. Zhou, K. Wongtchotigul, C. Taylor, and G. L. Harris, Mater. Sci. Eng. B 46, 147 (1997).

<sup>5</sup>K.-H. Wu, Y.-K. Fang, J.-H. Zhou, and J.-J. Ho, Jpn. J. Appl. Phys. **36**, 5151 (1997).

<sup>6</sup>E. W. Kiewra and P. C. Wayner, J. Electrochem. Soc. **136**, 740 (1989).

<sup>7</sup>A. Pèrez-Tomás, M. R. Jennings, M. Davis, J. A. Covington, P. A. Mawby, V. Shah, and T. Grasby, J. Appl. Phys. 102, 14505 (2007).

<sup>8</sup>A. N. Nazarov, Ya. N. Vovk, V. S. Lysenko, V. I. Turchanikov, V. A. Scryshevskii, and S. Ashok, J. Appl. Phys. 89, 4422 (2001).

<sup>9</sup>P. M. Gammon, A. Perez-Tomás, M. R. Jennings, A. M. Sanchez, C. Fisher, S. T. Thomas, B. T. Donnellan, and P. A. Mawby, Mater. Sci. Forum 740–742, 1006 (2013).

<sup>10</sup>J. Liang, S. Nishida, M. Arai, and N. Shigekawa, Appl. Phys. Lett. **104**, 161604 (2014).

<sup>11</sup>H. Takagi, K. Kikuchi, R. Maeda, T. R. Chung, and T. Suga, Appl. Phys. Lett. **68**, 2222 (1996).

<sup>12</sup>M. M. R. Howlader, T. Watanabe, and T. Suga, J. Vac. Sci. Technol. B 19, 2114 (2001).

<sup>13</sup>J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, and N. Shigekawa, J. Appl. Phys. 114, 183703 (2013).

<sup>14</sup>F. A. Kish, D. A. Vanderwater, and M. J. Peanasky, Appl. Phys. Lett. 67, 2060 (1995).

<sup>15</sup>G. Lian, H. G. Xing, Y. Chang, and N. Fichtenbaum, Appl. Phys. Lett. 93, 112103 (2008).

16J. Kim, N. G. Toledo, S. Lal, J. Lu, T. E. Buehl, and U. K. Mishra, IEEE Electron Device Lett. 34, 42 (2013).

<sup>17</sup>P. M. Gammon, A. Perez-Tomás, M. R. Jennings, V. A. Shah, S. A. Boden, M. C. Davis, S. E. Burrows, N. R. Wilson, G. J. Roberts, J. A. Covington, and P. A. Mawby, J. Appl. Phys. 107, 124512 (2010).

<sup>18</sup>H. Hanafusa, A. Ohta, R. Ashihara, K. Maruyama, T. Mizuno, S. Hayashi, H. Murakami, and S. Higashi, Mater. Sci. Forum 778–780, 649 (2014).

<sup>19</sup>J. Robertson and B. Falabretti, J. Appl. Phys. **100**, 014111 (2006).

<sup>20</sup>A. Pèrez-Tomás, M. R. Jennings, M. Davis, J. A. Covington, P. A. Mawby, V. Shah, and T. Grasby, Microelectron. J. 38, 1233 (2007).

<sup>21</sup>S. M. Sze, in *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981), pp. 144–202.

<sup>22</sup>M. Yoshimoto, R. Araki, T. Kurumi, and H. Kinoshita, ECS Trans. 50, 61 (2013).